## Advanced Power Control System For Enhancing Second-Life Battery Energy Storage Systems Integration and Reliability

by Pablo Poblete

Thesis submitted to the University of Technology Sydney (UTS) in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Supervisor : Dr. Ricardo P. Aguilera Co-Supervisor : Dr. Yam P. Siwakoti External Supervisor : Dr. Javier Pereda (PUC)

> > September, 2024 Sydney, Australia

# Certificate of Authorship / Originality

I, Pablo Poblete, declare that this thesis is submitted in fulfilment of the requirements for the award of Doctor of Philosophy, in the School of Electrical and Data Engineering at the University of Technology Sydney.

This thesis is wholly my own work unless otherwise referenced or acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis.

I certify that the work in this thesis has not previously been submitted for a degree nor has it been submitted as part of the requirements for a degree at any other academic institution except as fully acknowledged within the text. This thesis is the result of a Collaborative Doctoral Research Degree program with Pontificia Universidad Católica de Chile.

This research is supported by the Australian Government Research Training Program.

Production Note:Signature:Signature removed prior to publication.

Date: Sunday 3<sup>rd</sup> November, 2024

To my family and especially to my wife Valentina.

# Acknowledgments

I would like to thank my supervisors, Dr. Javier Pereda and Dr. Ricardo Aguilera, for giving me the opportunity to participate in the dual-degree program and for your invaluable technical guidance. Thank you for the hours you spent reviewing my work and discussing new ideas. Your constant encouragement motivated me to work hard and never stop learning.

In addition, I would also like to thank the Agencia Nacional de Investigacion y Desarrollo (ANID) and the University of Technology Sydney for funding my PhD studies under the grant ANID/Doctorado Nacional/21201967 and UTS scholarships, respectively.

I am grateful to all my colleagues and friends I met in both research laboratories. Our endless discussions and new ideas always kept me interested in our research field and motivated. I would like to give special mention to Rodrigo, Sebastián, and Ignacio, whose collaboration and friendship have been a significant part of my journey.

Last but not least, I would like to express my deepest gratitude to my loving family. Your support and belief in me have always been essential to all of my achievements. To my wife, your love, support, and patience have been my greatest source of strength through both the good days and the bad ones. This achievement also belongs to you.

# Abstract

Electric power grids are rapidly transforming due to the increasing integration of variable renewable energy sources (RES), distributed generation, and new loads associated with electric vehicle (EV) charging stations. These changes bring several technical challenges related to grid stability and integrity, increasing the operational complexity of future grids.

One of the most promising solutions to mitigate some of the issues related to RES is using battery energy storage systems (BESS). BESS can absorb active power when there is a surplus of RES power generation and output this power when it is most convenient. Moreover, BESS can also operate as an energy backup and provide ancillary services to the grid, increasing the power system flexibility. However, the high investment costs of Lithium-ion batteries impose a relevant cost barrier to the widespread adoption of this technology.

Intending to provide a new energy storage alternative that can accelerate the transition towards RES, this thesis presents a novel Cascaded H-Bridge (CHB) converter control and modulation strategy for the effective integration of second-life BESS (SL-BESS) into the electrical grid. These systems use batteries that have reached the end of their first operational life but still retain sufficient capacity for another use in a less demanding application. In particular, this work gives special attention to optimal modulation techniques, and optimal current and state of charge control strategies for the CHB converter with battery packs directly connected to each H-Bridge sub-module.

Simulation and experimental results are provided to verify the effectiveness of the proposed modulation and control strategies for a three-phase CHB converter-based SL-BESS prototype formed by second-life Lithium-ion battery packs.

# Contents

| Al            | Abstract 1      |                                     |                                                                                   |    |  |

|---------------|-----------------|-------------------------------------|-----------------------------------------------------------------------------------|----|--|

| $\mathbf{Li}$ | st of           | Acron                               | yms                                                                               | 9  |  |

| 1             | $\mathbf{Intr}$ | troduction 1                        |                                                                                   |    |  |

|               | 1.1             | Batter                              | y Energy Storage System Components                                                | 12 |  |

|               |                 | 1.1.1                               | Battery and PCS                                                                   | 12 |  |

|               |                 | 1.1.2                               | Battery Management System                                                         | 19 |  |

|               |                 | 1.1.3                               | Energy Management System                                                          | 22 |  |

|               |                 | 1.1.4                               | Converter Control for Grid-Connected ac-dc Converters for $\operatorname{BESS}$ . | 22 |  |

|               |                 | 1.1.5                               | SoC Balancing Control Schemes for CHB Converters and MMCs $$                      | 23 |  |

|               | 1.2             | Motiva                              | ation and Research Vision                                                         | 29 |  |

|               | 1.3             | Resear                              | ch Proposal                                                                       | 30 |  |

|               | 1.4             | Major                               | Contributions of the Thesis                                                       | 31 |  |

|               | 1.5             | List of                             | Publications                                                                      | 32 |  |

|               | 1.6             | Thesis                              | Structure                                                                         | 35 |  |

| <b>2</b>      | Opt             | imal V                              | Variable-Angle PS-PWM Strategy for CHB Converters Oper-                           |    |  |

|               | atin            | ating with Inter-SM Power Imbalance |                                                                                   | 38 |  |

|               | 2.1             | Introd                              | $\operatorname{uction}$                                                           | 38 |  |

|               | 2.2             | Freque                              | ency Analysis of the CHB Converter Output Voltage Switching Har-                  |    |  |

|               |                 | monic                               | Components                                                                        | 42 |  |

|               | 2.3             | Propos                              | sed Predictive Optimal VA-PS-PWM                                                  | 44 |  |

|               |                 | 2.3.1                               | Continuous-time Dynamic Model of the CHB Converter Switching                      |    |  |

|               |                 |                                     | Harmonic Components in the Synchronous dq-Frame                                   | 44 |  |

|   |                                                                         | 2.3.2  | Proposed Discrete-time Dynamic Model for PS-angle Updates                                                                                     | 45 |  |

|---|-------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|   |                                                                         | 2.3.3  | Sequential Optimal Control Problem                                                                                                            | 47 |  |

|   |                                                                         | 2.3.4  | Proposed predictive OVA-PS-PWM Algorithm                                                                                                      | 50 |  |

|   | 2.4                                                                     | Simula | ation Results and Benchmarking                                                                                                                | 51 |  |

|   | 2.5                                                                     | Exper  | imental Verification                                                                                                                          | 53 |  |

|   |                                                                         | 2.5.1  | Experimental Setup                                                                                                                            | 53 |  |

|   |                                                                         | 2.5.2  | Selection of the Number of Iterations of the Proposed OVA-PS-PWM $$                                                                           |    |  |

|   |                                                                         |        | Algorithm                                                                                                                                     | 55 |  |

|   |                                                                         | 2.5.3  | Computational Burden                                                                                                                          | 56 |  |

|   |                                                                         | 2.5.4  | Experimental Results                                                                                                                          | 58 |  |

|   | 2.6                                                                     | Concl  | usions                                                                                                                                        | 61 |  |

| 3 | Offset-Free Optimal Control of CHB-SL-BESS Based on a Kalman Filter     |        |                                                                                                                                               |    |  |

|   | Har                                                                     | rmonic | Compensator                                                                                                                                   | 63 |  |

|   | 3.1                                                                     | Introd | luction                                                                                                                                       | 63 |  |

|   | 3.2                                                                     | CHB    | Converter Model and Standard Optimal Control                                                                                                  | 66 |  |

|   |                                                                         | 3.2.1  | Continuous-Time Dynamic Model                                                                                                                 | 67 |  |

|   |                                                                         | 3.2.2  | Discrete-Time Dynamic Model                                                                                                                   | 68 |  |

|   |                                                                         | 3.2.3  | Optimal Control Problem and Steady-State Control Input Reference                                                                              |    |  |

|   |                                                                         |        | Design                                                                                                                                        | 69 |  |

|   |                                                                         | 3.2.4  | Effect of Unmeasured SM Capacitor Voltage Ripples                                                                                             | 70 |  |

|   | 3.3                                                                     | Propo  | sed KF-based Steady-State Error Compensation Strategy                                                                                         | 72 |  |

|   |                                                                         | 3.3.1  | Proposed Augmented State-Space Dynamic Model                                                                                                  | 73 |  |

|   |                                                                         | 3.3.2  | Proposed KF-based Compensation Strategy                                                                                                       | 75 |  |

|   | 3.4                                                                     | Exper  | imental Verification                                                                                                                          | 78 |  |

|   |                                                                         | 3.4.1  | Experimental Setup                                                                                                                            | 78 |  |

|   |                                                                         | 3.4.2  | Steady-State Performance Benchmarking                                                                                                         | 79 |  |

|   |                                                                         | 3.4.3  | Transient Performance                                                                                                                         | 85 |  |

|   | 3.5                                                                     | Concl  | usions                                                                                                                                        | 86 |  |

| 4 | Dual-Stage MPC for SoC Balancing in SL-BESS Based on $\Delta$ -CHB Con- |        |                                                                                                                                               |    |  |

|   | vert                                                                    | ters   |                                                                                                                                               | 88 |  |

|   | 4.1                                                                     | Introd | $uction \ldots \ldots$ | 88 |  |

|   |                                                                         |        |                                                                                                                                               |    |  |

|   | 4.2 SoC Balancing in $\Delta$ -CHB Converters |         | $ a lancing in \Delta - CHB Converters \dots \dots$ |

|---|-----------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                               | 4.2.1   | Discrete-Time SoC Dynamic Model                                                                                                                           |

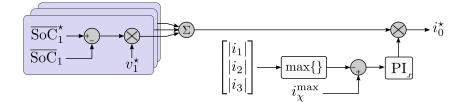

|   | 4.3                                           | Propo   | sed Dual-Stage MPC Strategy for SoC Balancing in $\Delta\text{-CHB-BESS}$ 94                                                                              |

|   |                                               | 4.3.1   | Proposed Inter-arm Energy Balance Optimization Stage 95                                                                                                   |

|   |                                               | 4.3.2   | Proposed Inter-SM Energy Balance Optimization Stage 100                                                                                                   |

|   | 4.4                                           | Contro  | bl Effort Analysis and Simulation Results                                                                                                                 |

|   |                                               | 4.4.1   | Unconstrained Solution for the Battery Currents                                                                                                           |

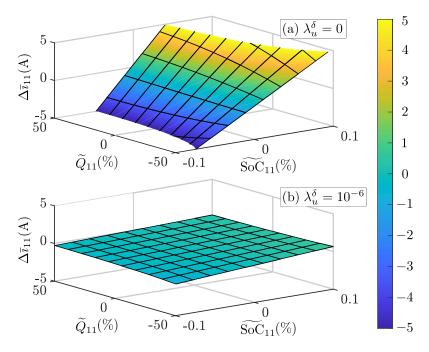

|   |                                               | 4.4.2   | Control Effort Analysis for the Unconstrained Battery Current Solution $107$                                                                              |

|   | 4.5                                           | Simula  | ation Results and Benchmarking                                                                                                                            |

|   |                                               | 4.5.1   | Impact of Weighting Factors and Steady-state Performance $\ . \ . \ . \ 110$                                                                              |

|   |                                               | 4.5.2   | Comparison With Different SoC Balancing Methods $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                  |

|   | 4.6                                           | Exper   | imental Verification                                                                                                                                      |

|   |                                               | 4.6.1   | Experimental Setup 114                                                                                                                                    |

|   |                                               | 4.6.2   | Weighting Factor Selection                                                                                                                                |

|   |                                               | 4.6.3   | Control Input Rate of Change Constraints Design $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                  |

|   |                                               | 4.6.4   | Experimental Results                                                                                                                                      |

|   | 4.7                                           | Conclu  | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $120$                                                                      |

| - | C                                             |         | 100                                                                                                                                                       |

| 5 | Con                                           | nclusio |                                                                                                                                                           |

|   | 5.1                                           | Conclu  | usions                                                                                                                                                    |

|   | 5.2                                           | Recon   | nmendations for Further Research                                                                                                                          |

# List of Figures

| 1.1  | BESS main components                                                                       | 13 |

|------|--------------------------------------------------------------------------------------------|----|

| 1.2  | BESS based on the conventional 2L-VSC                                                      | 14 |

| 1.3  | Three-level converter topologies.                                                          | 15 |

| 1.4  | Front-end inverter with controllable dc-link topologies. (a) modules are                   |    |

|      | connected in series (cascaded connection), and (b) modules are connected                   |    |

|      | in parallel                                                                                | 16 |

| 1.5  | CHB converter-based BESS with BPs directly connected to the SMs. (a)                       |    |

|      | star configuration, (b) delta configuration                                                | 17 |

| 1.6  | MMC-based BESS with BPs directly connected to the SMs                                      | 19 |

| 1.7  | Classification of the main SoC estimation methods                                          | 21 |

| 1.8  | Inter-arm energy balancing methods for cascaded multilevel converters                      | 24 |

| 1.9  | Conventional modulation strategies for cascaded multilevel converters ap-                  |    |

|      | plied to a single-phase CHB converter of 2 SMs                                             | 26 |

| 1.10 | Standard inter-SM energy balancing strategies classification for cascaded                  |    |

|      | multilevel converters based on the modulation scheme                                       | 27 |

| 2.1  | CHB converter arm with $n$ SMs using PS-PWM with unipolar modulation.                      | 39 |

| 2.2  | Representation of the $h$ -st output voltage harmonic component for a 3-SM                 |    |

|      | CHB converter in the rotating synchronous $dq$ -frame for conventional PS-                 |    |

|      | angles. (a) balanced operation, (b) unbalanced operation. $\ldots$ $\ldots$ $\ldots$       | 43 |

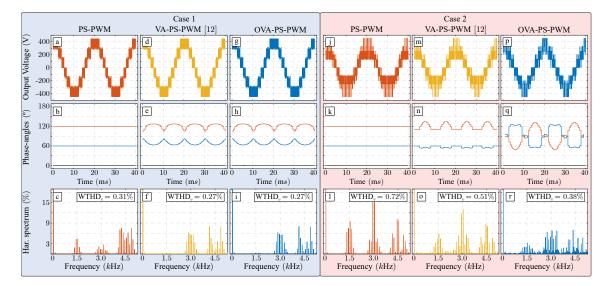

| 2.3  | CHB output voltage, PS-angles, and voltage harmonic spectra for the sim-                   |    |

|      | ulated cases 1 and 2                                                                       | 52 |

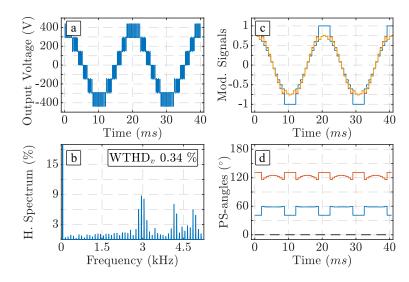

| 2.4  | Simulation results for the proposed OVA-PS-PWM working as a discontinu-                    |    |

|      | ous PWM technique. (a) CHB output voltage, (b) voltage harmonic spectra,                   |    |

|      | (c) ac modulating signals, and (d) PS-angles. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 53 |

|      |                                                                                            |    |

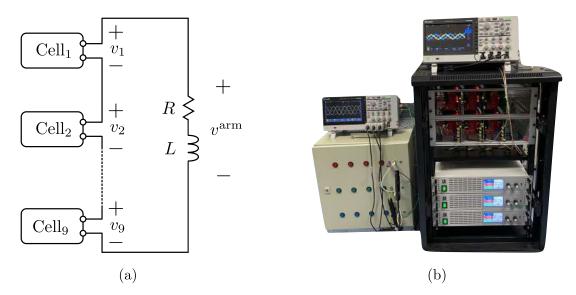

| 2 | .5  | Experimental setup. (a) circuit diagram, (b) experimental setup including                                                                                                       |    |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | the single-phase nine-cell CHB converter with isolated dc power supplies to                                                                                                     |    |

|   |     | feed the dc voltages of the SMs                                                                                                                                                 | 54 |

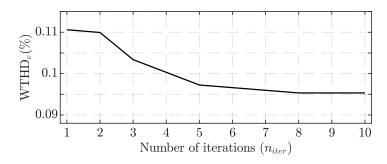

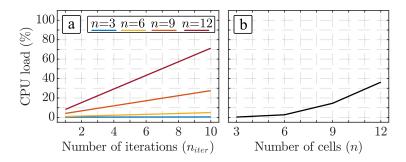

| 2 | .6  | Simulation results for the impact of the number of iterations of the OVA-                                                                                                       |    |

|   |     | PS-PWM algorithm in the CHB output voltage WTHD                                                                                                                                 | 56 |

| 2 | .7  | Execution time of the proposed OVA-PS-PWM in percentages of the total                                                                                                           |    |

|   |     | available time. (a) CPU load for different number of SMs and iterations,                                                                                                        |    |

|   |     | (b) CPU load for 8 iterations for different number of SMs                                                                                                                       | 57 |

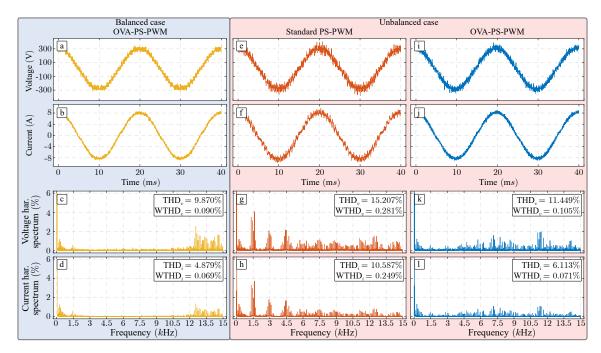

| 2 | .8  | CHB output voltage and current waveforms with their corresponding har-                                                                                                          |    |

|   |     | monic spectra for three experimental tests. The left column (a, b, c and d)                                                                                                     |    |

|   |     | shows the case with balanced operation conditions for the OVA-PS-PWM,                                                                                                           |    |

|   |     | the middle column (e, f, g and h) shows the conventional PS-PWM under                                                                                                           |    |

|   |     | unbalanced operation conditions, and the right column (i, j, k and f), shows                                                                                                    |    |

|   |     | the performance of the OVA-PS-PWM for the same unbalanced operation                                                                                                             |    |

|   |     | conditions                                                                                                                                                                      | 57 |

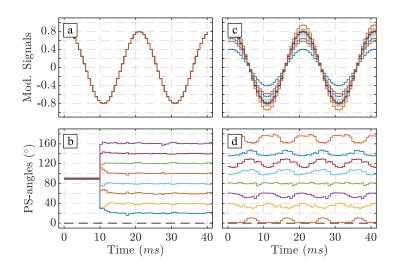

| 2 | .9  | PS-angles and modulating signals for the experimental results. (a)-(b) shows                                                                                                    |    |

|   |     | the convergence of the proposed OVA-PS-PWM for the balanced case. (c)-                                                                                                          |    |

|   |     | (d) shows the steady-state signals for the unbalanced case                                                                                                                      | 59 |

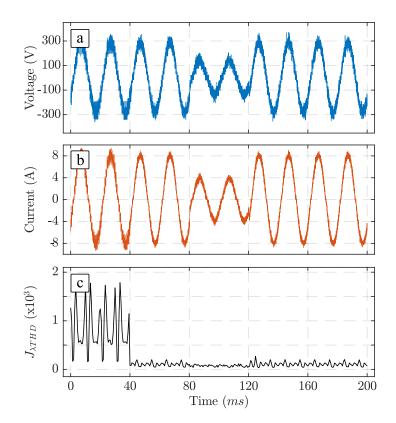

| 2 | .10 | Transient response of the proposed OVA-PS-PWM after enabled at $40\mathrm{ms}.$                                                                                                 |    |

|   |     | (a) CHB output voltage, (b) output current, (c) instantaneous cost function                                                                                                     |    |

|   |     | $J_{\lambda \text{THD}}(k)$ value                                                                                                                                               | 61 |

| 3 | .1  | Delta-connected CHB converter with $n$ power cells                                                                                                                              | 67 |

| 3 | .2  | Equivalent continuous-time circuit diagram of the augmented state-space                                                                                                         |    |

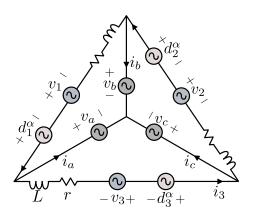

|   |     | model for the CHB converter, where $d_{\chi}^{\alpha} = (d_{\chi 1}^{\alpha} + d_{\chi 3}^{\alpha} + d_{\chi 5}^{\alpha}) \frac{r\gamma}{L(\gamma-1)}, \ \gamma = e^{T_s r/L}.$ | 75 |

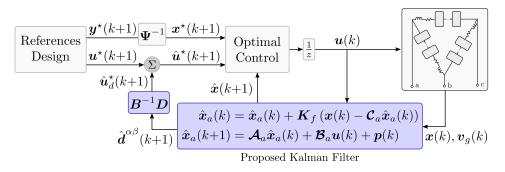

| 3 | .3  | Block diagram of the proposed KF observer for steady-state error compen-                                                                                                        |    |

|   |     | sation.                                                                                                                                                                         | 77 |

| 3 | .4  | Three-phase CHB-BESS converter prototype                                                                                                                                        | 78 |

|   |     |                                                                                                                                                                                 |    |

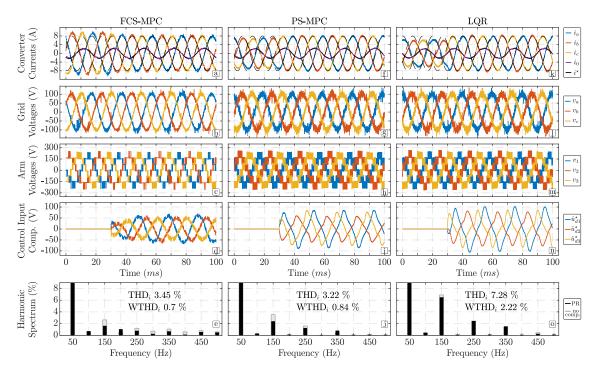

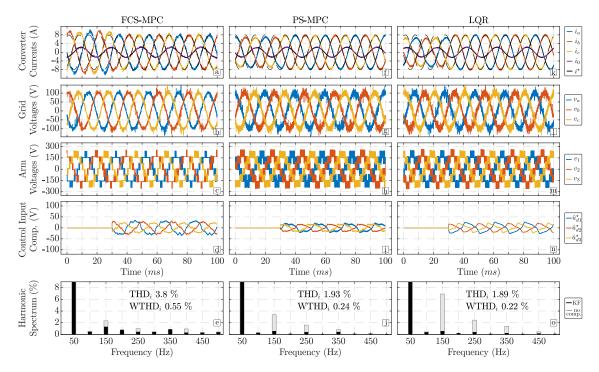

- 3.5 Experimental results with constant arm power references of  $P_1=P_3=500$  W,  $P_2=200$  W, Q=0 VAr, and the PR-based compensation strategy [103]. (a)-(e) shows the results for the FCS-MPC, (f)-(j) shows the results for the PS-MPC, and (k)-(o) shows the results for the LQR. The last row shows the harmonic spectrum of  $i_a$  with and without the compensation strategy.

- 3.6 Experimental results with constant arm power references of  $P_1=P_3=500$  W,  $P_2=200$  W, Q=0 VAr, and the proposed KF harmonic compensator. (a)-(e) shows the results for the FCS-MPC, (f)-(j) shows the results for the PS-MPC, and (k)-(o) shows the results for the LQR. The last row shows the harmonic spectrum of  $i_a$  with and without the compensation strategy. . . . 81

80

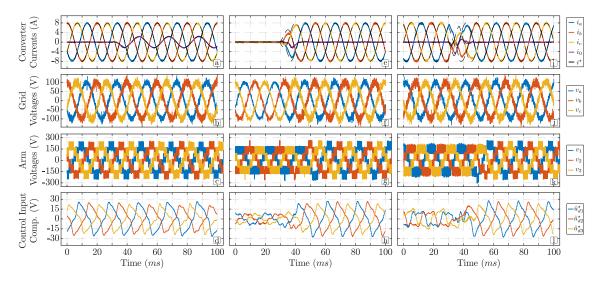

3.7 Experimental results for the proposed KF strategy under transients for an LQR. (a)-(d) shows a transient response for a circulating current step change, (e)-(h) shows an active power reference change of 1.2 kW, and (j)-(l) shows transient reversing the power flow from -1.2 kW to 1.2 kW.

85

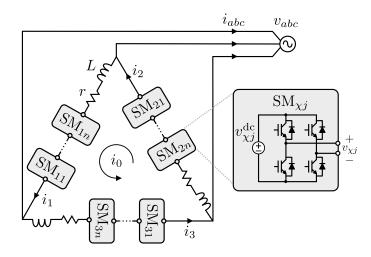

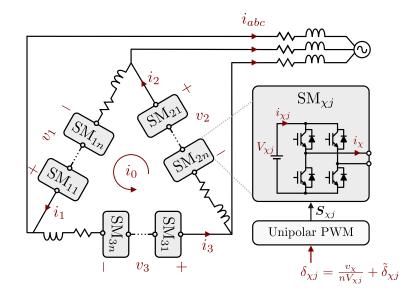

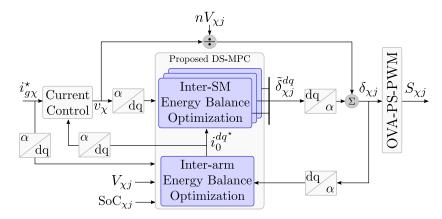

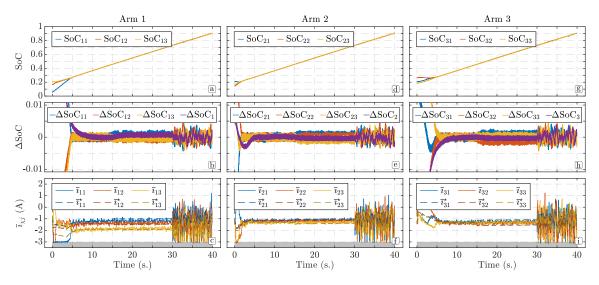

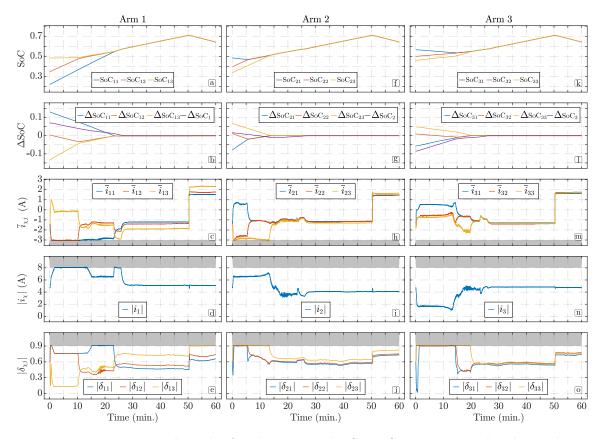

### Current and voltage definitions for the three-phase $\Delta$ -CHB converter topol-4.1 ogy with n SMs per arm and batteries directly connected to each SM ana-91 4.2Proposed DS-MPC scheme for optimal SoC balancing in $\Delta$ -CHB-BESS. . . 944.3Numerical example of the current error at the unconstrained battery current solution due to disturbances in the capacity values and SoC estimates. (a) dead-beat solution, (b) proposed DS-MPC strategy inter-SM solution. . . . 109 Simulation results for the proposed DS-MPC strategy. Each column shows 4.4 the signals related to a different $\Delta$ -CHB converter arm. The first row shows the battery SoCs. The second row shows the SoC error for each SM, $\Delta SoC_{\chi i}$ , and the arm SoC error, $\Delta SoC_{\chi}$ . The third row shows the battery currents and their steady-state references for a minimum allowed current of -3 A.

Disturbances in the capacity values are introduced after 15 s, and  $\lambda_u^{\delta}$ ,  $\lambda_u^{i0}$  are

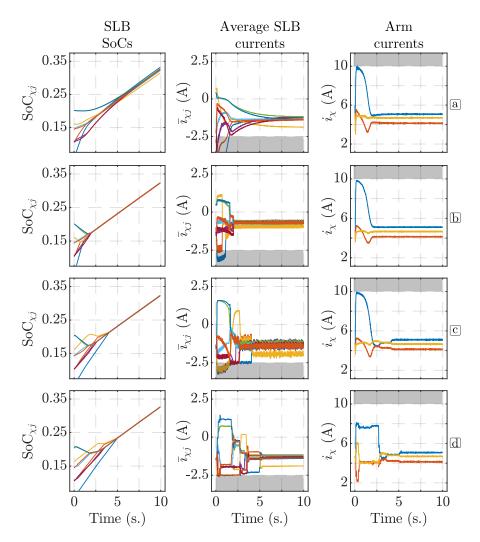

| $4.6  {\rm Simulation\ results\ for\ different\ SoC\ balancing\ methods.} \ (a)\ {\rm PI-based\ methods.}$ |                                                                                                                  |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                                                                            | [76], (b) sorting-based method [125], (c) MPC strategy [112], and (d) pro-                                       |

|                                                                                                            | posed DS-MPC strategy. The shadowed areas represent the imposed safety                                           |

|                                                                                                            | constraint thresholds. $\ldots$ |

| 4.7                                                                                                        | $\Delta\text{-CHB-BESS}$ experimental prototype with 9 SMs and SLBs 115                                          |

| 4.8                                                                                                        | Experimental results for the proposed DS-MPC strategy. Each column                                               |

|                                                                                                            | shows the signals related to a different $\Delta$ -CHB converter arm. The first                                  |

|                                                                                                            | row shows the SLB estimated SoCs, the second row shows the SoC errors                                            |

|                                                                                                            | for each SLB, and the average SoC error of the arm, the third row shows the                                      |

|                                                                                                            | SLB currents, the fourth row shows the amplitude of each arm current, and                                        |

|                                                                                                            | the fifth row shows the amplitude of each modulating signal. The shadowed                                        |

|                                                                                                            | areas represent the DS-MPC constraint thresholds                                                                 |

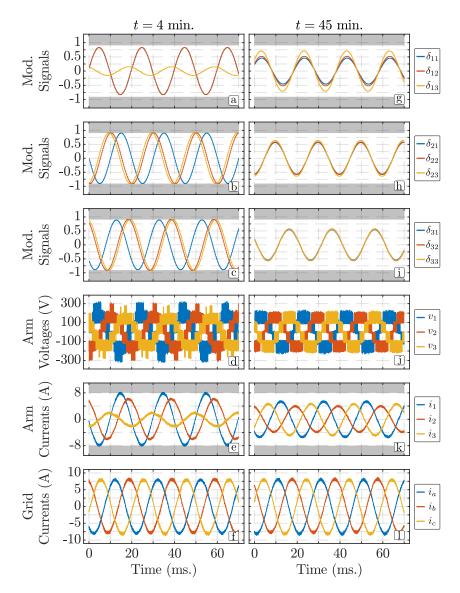

| 4.9                                                                                                        | Experimental results for the $\Delta$ -CHB waveforms at the beginning and end                                    |

|                                                                                                            | of the experimental test. The left column shows the converter signals at the                                     |

|                                                                                                            | beginning of the balancing test. The right column shows the signals close                                        |

|                                                                                                            | to the end of the test after the SoC balance was achieved                                                        |

# List of Acronyms

| RES                | : renewable energy sources.                                    |

|--------------------|----------------------------------------------------------------|

| $\mathbf{EV}$      | : electric vehicle.                                            |

| BESS               | : battery energy storage system.                               |

| LIB                | : Lithium-ion battery.                                         |

| BP                 | : battery pack.                                                |

| SL-BESS            | : second-life battery energy storage system.                   |

| CHB-BESS           | : cascaded H-Brdige based battery energy storage system.       |

| $\Delta$ -CHB-BESS | : delta-connected CHB-BESS.                                    |

| BMS                | : battery management system.                                   |

| $\mathbf{EMS}$     | : energy management system.                                    |

| PCS                | : power conversion system.                                     |

| $\mathbf{SoC}$     | : state of charge.                                             |

| $\mathbf{SoH}$     | : state of health.                                             |

| 2L-VSC             | : two-level voltage source converter.                          |

| CHB                | : cascaded H-Bridge.                                           |

| $\mathbf{SM}$      | : sub-module.                                                  |

| $\mathbf{PR}$      | : proportional-resonant.                                       |

| PI                 | : proportional-integral.                                       |

| MPC                | : model predictive control.                                    |

| DS-MPC             | : dual-stage model predictive control.                         |

| $\mathbf{QP}$      | : quadratic program.                                           |

| KF                 | : kalman filter.                                               |

| PS-PWM             | : phase-shifted pulse width modulation.                        |

| PS-angle           | : PWM carrier phase-shift angle.                               |

| OVA-PS-PWM         | : optimal variable-angle phase-shifted pulse width modulation. |

|                    |                                                                |

## Chapter 1

# Introduction

Nowadays, there is an increasing global concern for reducing fossil fuel reliance by promoting generation technologies related to clean and renewable energy sources (RES), such as solar photovoltaic (PV) and wind turbines. This tendency in the generation sector is being carried out not only for the RES capability to reduce carbon emissions but also for its capability to promote economic growth [1], [2]. Consequently, the global renewable power capacity is expected to be expanded by 50% between 2019 and the end of this year [3]. Moreover, this increasing trend in RES should be sustained in the following decades, as Chile, Australia, USA, and EU governments have announced their target to reach zero carbon emissions by 2050, while China aims to reach this target by 2060.

The intermittent nature of some RES and new types of loads, such as electric vehicles (EVs) charging stations, variable-speed drives, power supplies, and light-emitting diode drivers, have brought new technical challenges to the grid stability and its operation [4], [5]. These challenges are related to the temporal energy mismatch between local generation and consumption, which can affect the output power quality of the grid, i.e., the ability of the electrical system to create an ideal power supply with a pure noise-free sinusoidal waveform [6]. Poor power quality leads to disturbances in the power flow through transmission lines, increasing power losses and conditioning the continuity of service in the most severe cases. As a consequence, significant operating reserves are required to meet the demand in case of sudden variations in the output of RES, which causes an increase in the operational cost and complexity of the electricity network [4]. Some of the expected power quality issues associated with a high RES penetration include the fluctuation in voltage, increased

reactive power flow, harmonics injection, and excessive neutral currents [7].

A solution to enhance grid stability despite high RES adoption levels is to use battery energy storage systems (BESS), which have attracted the scientific community and the industry attention in recent years [4]. BESS can provide multiple services to grid operators, distributed generators, energy retailers, and consumers [8], [9]. For instance, BESS can absorb active power to charge the batteries when there is a surplus of RES power generation and output this power when it is most convenient. Furthermore, BESS can provide operating reserves and allow the creation of new revenue models for existing RES-based power generators, such as energy arbitrage, peak-shaving, and voltage and frequency control.

Despite the technical benefits obtained by incorporating BESS into the electrical grid, the high investment cost of new batteries is still a prominent barrier that limits the massive integration of this technology. Accordingly, developing profitable projects is challenging if the energy prices are not increased or new monetary incentives for ancillary services are not introduced. Hence, the economic viability of BESS is still unclear for the following years for some energy markets [10].

On the other hand, the world has initiated a revolution in transportation electrification, in which the EV market has shown exponential growth in recent years [11]. Indeed, the number of EVs and hybrids in circulation will reach 130 million by 2030, based on the forecast presented in [3]. The first life of these EV batteries will be considered to be over after the warranty period of the EV, which usually is over after reaching more than 160,000 kms driven. After this period, the remaining energy capacity of the EV batteries tends to vary between 70% and 80% of their nominal value [12]. Furthermore, intact BPs or battery modules from crashed EVs can exhibit higher remaining energy capacities by the end of their first life due to reduced aging [13].

Consequently, this significant remaining capacity, together with the high energy density and long life of Lithium-ion batteries (LIBs) [14], makes the LIBs, discarded from the EV market, attractive for their reuse in grid-connected second-life battery (SLB) energy storage applications. Moreover, this reutilization offers substantial environmental and economic benefits [15].

SLB costs are significantly lower than new batteries, while they retain most of their performance capabilities [16]. As a result, these batteries can potentially overcome the high investment cost barrier of BESS. Furthermore, SLB applications are expected to play a crucial role in the next decade by giving more time to the recycling industry to scale up the technology required to effectively recycle LIBs [17].

One of the major challenges of creating high-power second-life BESS (SL-BESS) is related to the fact that incorrect handling of LIBs with different capacities can lead to inefficient use of the available stored energy. Moreover, inadequate LIBs charging/discharging operations might lead to significant safety risks, with one of the most severe consequences being battery incineration due to thermal runaway [18]. Therefore, the performance and safety concerns related to LIBs become more prominent in SL-BESS than in standard BESS, as SLBs can present significant differences among battery modules. For instance, an SL-BESS can contain batteries from different EV models and/or batteries with different degradation levels. In this sense, special attention must be given to the power converters and control algorithms that can allow the efficient and safe integration of SLBs into the electrical grid.

The following section reviews the main topics related to BESS and SL-BESS applications used in industry or proposed in the current literature.

### **1.1** Battery Energy Storage System Components

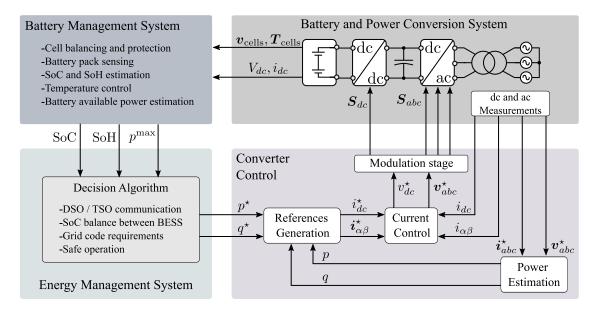

In this section, the main components of a BESS are described and grouped into four categories: 1) battery and power conversion system (PCS), 2) battery management system (BMS), 3) energy management system (EMS), and 4) converter control. A diagram of these categories is illustrated in Fig. 1.1.

#### 1.1.1 Battery and PCS

Power electronics is the key enabling technology allowing the connection of BESS to the electricity grid [19]. The PCS serves as the interface between the battery dc-voltage and the grid ac-voltage. Therefore, it enables the controlled, secure, and efficient power exchange between the batteries and the system they are connected to [20]. In this way, the PCS allows the BESS to meet grid codes and standards when providing services to the energy market [4].

The nominal voltage of electrochemical cells is very low concerning the required grid connection voltages. Taking Lithium-ion cells as an example, they typically have nominal

Figure 1.1: BESS main components.

voltages of 3.2 V - 3.6 V for Lithium Iron Phosphate (LFP) chemistry and 3.6 V for Lithium Cobalt Oxide (LCO), Lithium Nickel Cobalt Aluminum Oxide (NCA), and Lithium Nickel Manganese Cobalt Oxide (NMC) chemistries. Additionally, the capacity of commercially available cells is usually limited to a few hundred Ah or less. As a consequence, several cells must be connected in series and parallel to achieve the desired power and energy capacity requirements of a grid-connected BESS.

The trade-off regarding how many cells to wire in series versus in parallel to achieve the battery pack (BP) maximum power design requirements is generally determined by several factors, such as manufacturing economics and BP safety, volume, and modularity [18], [20]. A higher BP voltage for the same power reference leads to a lower battery current. Hence, the conduction losses are reduced for the same output power. However, the series connection of cells requires specialized balancing and measuring circuits installed as part of the BMS, increasing its complexity. These balancing circuits for series-connected cells are required to compensate for their energy capacity imbalance and to operate the battery pack efficiently and safely [21], [22]. If the cell balance condition is not met, then one or more cells have a state of charge (SoC) that is too high or too low regarding others, leading to a reduced effective energy capacity of the pack, increased capacity fading of cells, or even safety hazards [18], [23].

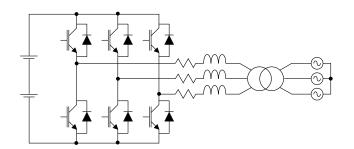

Figure 1.2: BESS based on the conventional 2L-VSC.

The factors mentioned above involved in the battery pack design have led researchers to propose several PCS topologies for integrating BESS into the electrical grid [4], [20], [24]. The different features of some of the most popular topologies are discussed in the following section.

#### Conventional 2L and 3L Voltage Source Converters

The two-level voltage source converter (2L-VSC) is shown in Fig. 1.2. This configuration is currently the industry's preferred choice for interfacing BESS with the grid [8]. However, an additional line frequency transformer is required to connect the BESS to medium/high voltage transmission lines, which is bulky, costly, and it introduces additional losses. Despite these drawbacks, this transformer offers the advantage of limiting the rise time of short-circuit currents, helping the converter protection system. In this way, the 2L-VSC handles the bidirectional power flow between the battery and the ac grid, whereas the transformer boosts the voltage of hundreds of volts of the battery pack to medium voltage (MV) levels, i.e., tens of KVs.

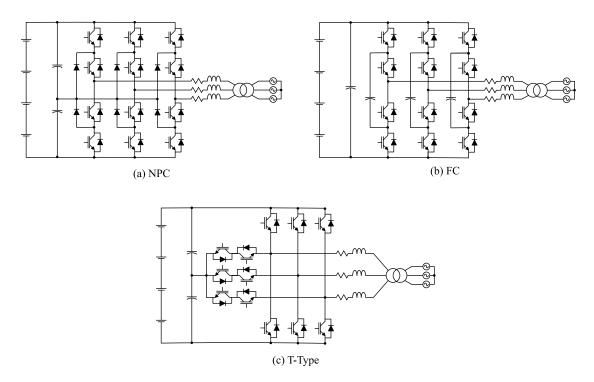

The same scheme can be applied to the conventional three-level voltage source converters (3L-VSCs) topologies, such as neutral point clamped (NPC), flying capacitor (FC), and T-Type converters [8], [24], which are shown in Fig. 1.3. The extra level of these converters allows an extra degree of freedom at the converter output voltage magnitude, improving the harmonic distortion and reducing the switching frequency. However, this benefit comes at the expense of using more semiconductor devices and more complicated control and modulation schemes [25], [26].

Many BPs with their respective 2L or 3L-VSCs must be connected in parallel to create a large-scale BESS with power ratings of several MWs. The main advantage of this config-

Figure 1.3: Three-level converter topologies.

uration is its high reliability and decoupled control of the BP power references [20]. Indeed, the failure in one BP or PCS does not necessarily lead to the whole system's interruption under this configuration, and each PCS can be easily disconnected from the rest of the system through a conventional voltage breaker.

The major limitation of these topologies for SL-BESS is related to the fact that large BPs are required to reach a minimum dc voltage level needed for connecting the inverter to the ac grid, which increases the BMS complexity [27]. Moreover, manufacturing these packs might not be feasible with SLBs, as the direct series or parallel connection of batteries with a different state of health (SoH) can lead to hazardous conditions. In fact, the direct connection of batteries with different capacity or internal resistance values, or the replacement of particular cells within an existing BP, is almost universally disapproved of by BESS manufacturers [28]. Accordingly, using these topologies with second-life BPs of reduced power and voltage might require extra semiconductor devices to boost the dc voltage. Moreover, connecting each second-life BP to independent inverters might also increase the PCS costs as these packs cannot easily reach hundreds of kW for prolonged periods of time.

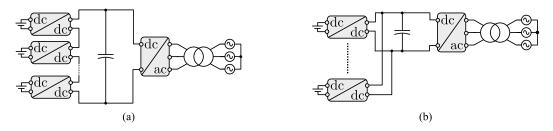

Figure 1.4: Front-end inverter with controllable dc-link topologies. (a) modules are connected in series (cascaded connection), and (b) modules are connected in parallel.

#### Front-End Conventional Inverter Topology with Controllable dc-link

A different approach for reducing the BMS complexity is to divide the BP into smaller modules by using dc-dc converters with a cascaded or parallel connection. This configuration creates a controllable dc-link connected to a front-end 2L- or 3L-VSC, as shown in Fig. 1.4.

The reliability of these configurations is analyzed in [20]. Here, the cascaded connection showed the weakest configuration, as its efficiency is the lowest and it requires more complex active SoC balancing control schemes to connect battery modules of different capacities. Moreover, the dc-link voltage range is compromised by the failure of individual battery modules. As a result, the reliability and flexibility of the SL-BESS might deteriorate under this topology if the BP is divided into only a reduced number of battery modules.

On the other hand, better results in terms of efficiency and reliability were obtained for the parallel connection of battery modules to a front-end inverter [20]. The increase in reliability is due to each dc-dc converter independently controlling the current profile of its battery module. Therefore, batteries of different capacities and power ratings can be included in independent SMs, and their SoC can be balanced using conventional control schemes.

#### **Cascaded H-Bridge Converter**

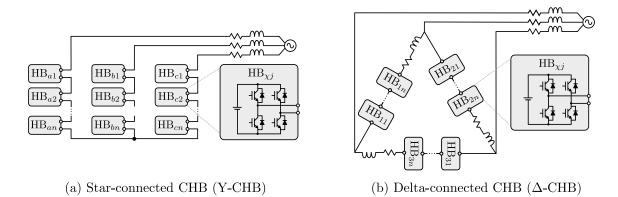

The cascaded H-bridge converter (CHB) consists of three-phase arms, where each arm is formed by the series connection of multiple H-bridge (HB) sub-modules (SMs) and a filter inductor. These arms can be connected in either star (Y-CHB) or delta ( $\Delta$ -CHB) configuration as illustrated in Fig.1.5. The modular structure of the CHB converter allows this topology to be directly connected to higher ac output voltage levels and provide

Figure 1.5: CHB converter-based BESS with BPs directly connected to the SMs. (a) star configuration, (b) delta configuration.

fault-tolerant capabilities. In fact, the scalability of the CHB converter enables the transformerless connection of this converter to the MV grid with less harmonic distortion and reduced switching losses without increasing the voltage rating of individual switching devices [29].

In addition, the modular structure of the CHB allows the separation of the BP into smaller modules with fewer series-connected cells at their battery strings, decreasing the complexity of the BMS. Besides, the CHB converter allows uneven power distribution among its arms and its SMs, enabling the active balance of SoC among BPs [27], [30]. In this sense, EV BPs can be directly connected to independent converter SMs, allowing their integration without a significant intervention of the original packs. Alternatively, a dc-dc converter stage can be considered to interface each battery with the CHB converter SMs. However, this extra power conversion stage per BP can increase the converter cost, making it less attractive against the conventional 2L-VSC [4].

In [4], an efficiency and cost analysis for BESS converter topologies was carried out. The results of this analysis indicate that the transformerless CHB converter is the most affordable PCS for integrating BESS into the MV grid and exhibits lower losses than conventional 2L- and 3L-VSCs. These advantages and the capacity of the CHB converter to provide uneven power distribution among its SMs make this topology a promising alternative for next-generation SL-BESS inverters [20].

Nevertheless, the unbalanced power distribution among SMs poses additional challenges to the control system of the CHB converter [31], [32]. If the active power references are not properly assigned among SMs, the battery with the lowest capacity might reach its minimum SoC threshold considerably faster than the others [33], limiting the performance of the BESS. Furthermore, the CHB converter has a limited capability to assign unbalanced power reference to its SMs [31]. Thus, neglecting these power limits in the SoC balancing control strategy deteriorates the converter current control tracking and may lead to undesired harmonic distortion due to overmodulation or even harm some batteries.

Finally, a potential issue of the CHB topology that has been recently investigated is the impact of the current ripple at the battery port when the batteries are directly connected to the HB-SMs. Two main ripple components can be identified in the battery port. One component is related to the high-frequency pulse-width modulation (PWM), whereas the other is given by the pulsating power injected by each converter leg at the double ac frequency of the grid. Accordingly, experimental results indicate that the current ripples might accelerate the capacity fade of the batteries if the ripple brings a considerable increase in the operating temperature of the BPs [34]. Nevertheless, it remains unclear to this date whether these ripple components significantly affect the lifespan of batteries, provided that temperature is controlled and low current rates are used [35].

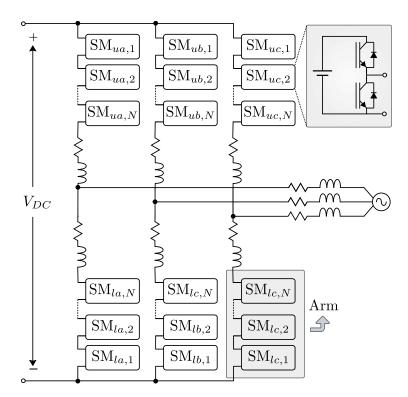

#### Modular Multilevel Converter

As depicted in Fig.1.6, the three-phase modular multilevel converter (MMC) consists of three legs connected in parallel to a common dc-bus. Each leg is divided into two arms named as upper and lower. These arms are formed by the series connection of SMs with a filter inductor. Each converter leg's midpoint is connected to an ac output filter. One of the main applications of the MMC is high-voltage direct-current (HVDC) systems [36], as the converter allows the direct connection to a high-voltage dc-grid. Nevertheless, this dc-voltage connection is not mandatory for BESS applications [37].

The MMC also allows for splitting the BP into smaller SMs, similar to the CHB converter. Therefore, active SoC balancing can be implemented [37]–[39]. Moreover, the MMC offers an extra degree of freedom for SoC balancing when compared to the CHB converter, which is given by the converter circulating currents, i.e., the currents that circulate through the clusters of each phase leg, but without appearing in the output currents [40].

The MMC shares challenges similar to those of the CHB converter regarding the control complexity of the SoC balancing algorithms and the active power reference distribution

Figure 1.6: MMC-based BESS with BPs directly connected to the SMs.

among SMs. Besides, the MMC requires a higher number of components [4]. Nonetheless, both the MMC and the CHB converter are considered promising candidates for integrating modular SL-BESS [31], [41]. Therefore, research efforts are being concentrated on developing new power-sharing strategies that ensure effective SoC balance for both converter topologies [20].

#### 1.1.2 Battery Management System

The BMS is an embedded system built specially to make the battery operation safe, reliable, and cost-effective [42]. In this sense, the BMS actively controls the BP functions to maximize its life by considering the maximum battery power and temperature ratings for its operation conditions. Moreover, the BMS is often responsible for providing accurate estimations of the battery SoC and SoH, which are reported to the EMS. Some of the main tasks usually performed by BMS are enumerated below [18]:

1. Protect the safety of the BESS: the BMS detects unsafe operating conditions, such as overcharge or overcurrent, and loss of insulation, disconnecting the battery pack from its output power terminals if necessary.

- 2. Battery-pack sensing: the BMS continuously senses each series-connected cell voltage, the BP current, and some cell temperatures.

- 3. SoC and SoH estimation: the BMS makes estimations of the cell's SoC and SoH based on the measured signals.

- 4. Battery pack power estimation: the BMS estimates the maximum power the battery pack can deliver at each instant by considering the configuration of the cells in the BP and its temperature.

#### **Battery SoC Estimation Methods**

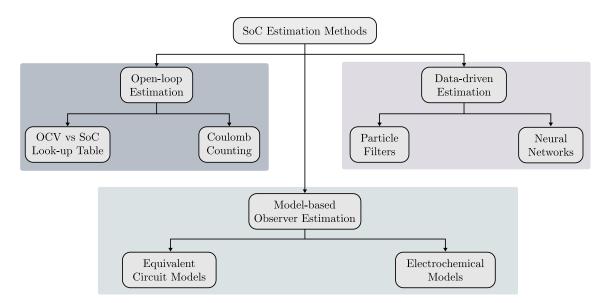

As previously mentioned, one of the primary functions of the BMS is calculating the battery SoC, which is an indicator that quantifies the remaining charge of a battery regarding its total capacity [43]. An accurate estimation of SoC produces additional benefits to the operation of the BP, such as promoting the longevity of the battery by avoiding over-charging and over-discharging. Moreover, precise SoC estimates improve the performance and power density of the battery by allowing the EMS to aggressively use the entire BP capacity [18].

The SoC estimation challenge arises since SoC cannot be directly measured in a battery. Therefore, it must be inferred from measurable variables, such as current, voltage, and temperature. A classification of the main SoC estimation methods is shown in Fig. 1.7.

Among the open-loop SoC estimation methods, the coulomb counting method is based on measuring the amount of charge added to or removed from the battery, leading to a straightforward implementation. However, this SoC estimation technique lacks a feedback signal to correct the state estimation. As a consequence, this method is susceptible to current sensor measurement errors, sensor noise, wrong SoC initialization, and errors in estimating the total capacity and coulombic efficiency parameters [18].

The open circuit voltage (OCV) look-up table method is based on performing SoC estimates based on a previously established relationship  $v(k) \approx \text{OCV}(z(k))$ , where v(k) is the terminal voltage of the cell, and z(k) refers to the battery SoC. This voltage and SoC relationship can be determined by slowly charging and discharging the battery for a full cycle [18]. Nevertheless, using an OCV look-up table only provides accurate estimates

Figure 1.7: Classification of the main SoC estimation methods.

when the battery is resting, i.e., after being disconnected from a load for several minutes. Thus, the OCV method in practice is only used to calculate the SoC initial condition for a different estimation method after a resting period [44].

Data-driven methods have attracted the interest of the research community lately due to the recent advances in machine learning, and the greater availability of battery data [45]. These methods can establish a relationship between the measured variables, and the SoC and SoH without any previous knowledge of the chemistry and characteristics of the battery [46]. However, these algorithms are susceptible to the training data selection and may present a poor performance when this data cannot completely cover the present operating conditions of the BP [43].

Finally, model-based estimation methods consist of using a battery model to predict the battery terminal voltage based on the cell voltages, current, and temperature measurements while applying an estimation algorithm to compute the SoC [47]. Several models of different complexity have been proposed and analyzed for optimal control applications in [46]. The equivalent circuit models are widely used for their satisfactory performance and low computational burden. More advanced and precise electrochemical models have also been proposed [46]. However, their high computational load requirements often challenge their application for real-time control purposes.

#### 1.1.3 Energy Management System

The EMS objective is to operate the BESS efficiently by optimally scheduling its operation and coordinating the multiple batteries and storage devices of the system, which can vary in size and technology [48]. The EMS collects from the BMS the battery status information and additional operational data such as measurements at the point of common coupling (PCC), energy market prices, weather forecasts, and commands from the distribution and transmission system operators [8].

Concerning the EMS control strategy, no solution emerges as the most common one, as there are many different BESS applications, such as peak shaving, renewable capacity firming, frequency regulation, and synthetic inertia, among others [8]. Nevertheless, model predictive control (MPC) strategies have been cataloged as promising techniques that can deal with the uncertainties of forecasts in multi-step optimization problems [49]–[51]. As a consequence, several MPC strategies for handling distributed BESS have been proposed in the field of microgrids, e.g., [49]–[54].

#### 1.1.4 Converter Control for Grid-Connected ac-dc Converters for BESS

The control for grid-connected converters is focused on regulating the power flow between the BESS and the grid by controlling the power semiconductor devices. Usually, the active and reactive power references for these control loops in BESS are determined by the EMS [48].

The conventional methods for governing grid-connected power converters are given by linear controllers generating continuous modulating signals. These signals are then transformed into high-frequency pulses using a modulation stage [55]. Among these control schemes are the classical proportional-integral (PI) regulators in the rotating synchronous dq-reference frame, and the proportional-resonant (PR) controllers implemented in  $\alpha\beta$ frame [56]. These control techniques are widely employed in several industrial applications due to their well-known design procedures. These techniques usually are categorized under the family of voltage-oriented control (VOC) schemes [57].

A different category of control methods for grid-connected ac-dc converters are direct power control (DPC) strategies. These techniques aim to directly govern the instantaneous active and reactive powers without using any inner-loop current regulator. Conventional DPC strategies obtain the switching actions from look-up tables and hysteresis comparators [58]. Nevertheless, the hysteresis comparators lead to variable switching frequency, complicating the passive filter design. A different approach is proposed in [59], where PI regulators control the active and reactive powers by generating synchronous dq-voltage references directly from the active and reactive power tracking errors.

Modern control schemes such as sliding mode control [60], artificial intelligence control [61], [62], MPC [63], are becoming more popular for power converters since the last decade. This trend has been motivated by the continuous progress in digital control platforms, e.g., digital signal processors (DSPs) and field programmable gate arrays (FPGAs). The improvements of these control methods over the classical ones are related to the better handling of non-linearities and improved dynamic performance.

The previously mentioned standard dc-ac control techniques can be directly applied to 2L- and 3L-VSC topologies with a centralized BP. However, in cascaded multilevel converters that distribute the battery modules within the converter power cells, additional control loops are required to balance the internal energy of the BESS among BPs. These SoC balancing control loops are crucial for SL-BESS due to differences in capacity, and the SM power references disparity constraints imposed by the cascaded multilevel converter topologies [31]. Accordingly, the following section reviews different control schemes for the internal energy balance designed specifically for these power converters.

#### 1.1.5 SoC Balancing Control Schemes for CHB Converters and MMCs

New control techniques have been developed in recent years to integrate BPs into multilevel converter topologies with cascaded cells, such as the CHB converter and the MMC. These control schemes are designed to track active and reactive power references to exchange power between the BESS and the electrical grid while providing an internal energy balance among SMs that regulates each BP SoC.

The necessity of closed-loop SoC balancing control schemes is related to the full utilization of the available energy in the BESS. Indeed, without active energy balancing among SMs, the battery with the lowest capacity, which is the first to reach 0% SoC during discharging, limits the BESS usable capacity. As a consequence, in this scenario, some BPs cannot be further discharged without over-discharging, which leads to permanent battery damage in the weakest BPs [18].

Figure 1.8: Inter-arm energy balancing methods for cascaded multilevel converters.

Both, the CHB converter and the MMC allow the SoC balancing control of the different BPs by regulating either the output power reference or the dc current for each SM. Therefore, batteries of different capacities or even SLBs of different manufacturers can be included in the same cascaded multilevel converter without necessarily limiting the system capacity to the weakest battery [64], [65]. Nevertheless, the maximum power imbalance among SMs is physically constrained in these converters as arbitrary power references for each cell are not feasible in many cases. These power limit constraints are not only given by the individual BP power ratings but also due to the coupling between the seriesconnected SMs, which share the same arm current [31]. Therefore, developing effective energy-balancing techniques for these converters adds complexity to the power converter control system.

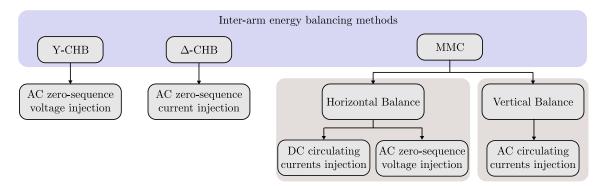

The SoC balance control problem in cascaded multilevel converters is usually divided into two sub-problems: the inter-arm energy balance and the inter-SM energy balance problem. These control problems are described in the sections below.

#### **Inter-arm Energy Balance**

The primary control objective of inter-arm energy balance strategies is to equalize the average stored energy among the arms of the converter [66]. In this sense, the inter-arm energy balance controller is generally designed without paying attention to the SoC of individual BPs [32]. As a consequence, the control system for standard inter-arm energy balancing strategies usually models the converter arms as ideal controlled voltage sources. In order to balance the energy among phases in cascaded multilevel converters, the inter-arm energy balance strategies provide additional arm currents or voltage references, which

can transfer active power among the arms without affecting the power exchange with the electrical grid.

The voltage or current injection needed to achieve inter-arm power imbalance depends on the converter topology. Accordingly, Fig. 1.8 summarizes the required signals to transfer power among arms for standard cascaded multilevel converters. The calculation of these voltage and current references for each converter are reviewed in [66], [67] for the MMC, and in [32], [68], [69] for the CHB converter. In general, these techniques can find the required circulating current or zero sequence voltage references to achieve the desired inter-arm power imbalance, by using phasor analysis or analytical solutions based on the converter power references and instantaneous measurements at the PCC.

#### **Inter-SM Energy Balance**

The main control objective for the inter-SM energy balancing schemes is to maintain each BP SoC equal to the average SoC of all the BPs connected within an arm [70]. In the case of SL-BESS, achieving the inter-SM SoC balance is challenging, as the active power distribution among SMs can be highly unbalanced due to differences in energy capacity. In this sense, the inter-SM SoC balance control ensures that batteries with larger capacities operate with larger currents. Moreover, it allows the SMs connected to malfunctioning SLBs to provide zero active power without requiring a major shutdown of the SL-BESS.

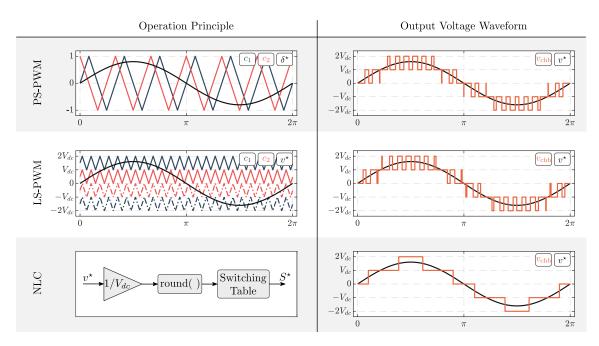

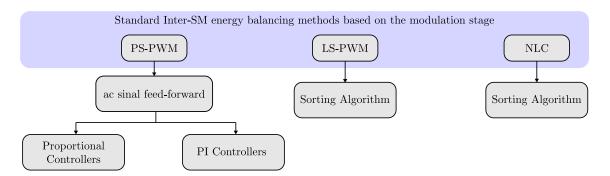

In contrast with the inter-arm energy balancing strategy, the inter-SM SoC balancing control schemes do not depend on the cascaded multilevel converter topology but on the modulation technique applied to the power cells. Accordingly, the conventional modulation stages and the classification of the inter-SM energy balance control techniques regarding the converter modulation stage for cascaded multilevel converters are summarized in Fig. 1.9 and Fig. 1.10, respectively.

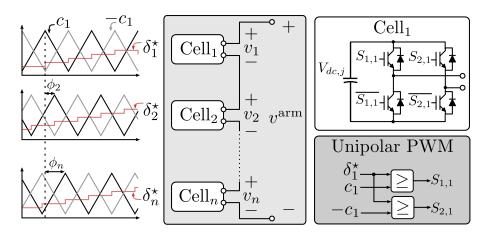

Phase-shifted pulsewidth modulation (PS-PWM) is one of the most popular modulation strategies for cascaded converters [71]. In this method, the switching signals for each SM are obtained using a standard PWM technique with a triangular carrier signal. A specific phase-shift-angle (PS-angle) is applied among the carriers to achieve the optimal harmonic performance [72]. As a result, the output voltage effective switching frequency of the cascaded converter becomes  $2nf_c$ , with n the number of SMs within each arm of the converter, and  $f_c$  the PWM carrier frequency.

Figure 1.9: Conventional modulation strategies for cascaded multilevel converters applied to a single-phase CHB converter of 2 SMs.

The level-shifted PWM (LS-PWM) strategy can also be applied to cascaded converters. However, its conventional implementation is not preferred over the PS-PWM for the MMC and the CHB converter due to the uneven switching and conduction losses among SMs [71]. The LS-PWM method vertically distributes the triangular carriers and compares them with the arm voltage reference. Thus, only one SM can change its output voltage during the sampling period while the others remain in a fixed switching state. In this way, the switching SM changes every time the modulating voltage requires a different output voltage level or if the vertical alignment of the carriers is modified [73].

Finally, the nearest level voltage control (NLC) offers an alternative approach to reduce the switching losses of PWM strategies in cascaded multilevel converters. This method generates the switching states of the SMs using the rounded value of the arm reference voltage, leading to a constant on/off operation for each semiconductor device during every sampling period [71]. Consequently, NLC reduces the switching frequency at the expense of higher harmonic distortion and increased error in generating the output voltage reference, which reduces the applicability of this method for converters of a reduced number of SMs [74].

Figure 1.10: Standard inter-SM energy balancing strategies classification for cascaded multilevel converters based on the modulation scheme.

One of the first inter-SM SoC balancing control schemes for PS-PWM was introduced in [30] for the CHB converter and implemented in a 500 kW project [75]. Here, the arm modulating voltage references are obtained using the classical current control scheme in the rotating synchronous dq-frame. However, instead of applying equal modulating voltages to each SM, their voltage references are individually adjusted by an additional feed-forward term. This term is based on proportional controllers that regulate the inter-SM SoC balance. The feed-forward terms are fed with SoC error signals, calculated as the difference between the individual SoCs and the arm average SoC. The outputs of the proportional controllers are multiplied by a sinusoidal signal in phase with the arm modulating voltage, effectively modifying the active powers of each BP to correct SoC balance errors.

Following the same principle, additional works that add a fundamental frequency ac component to each SM modulating signal have been proposed [76]–[78]. In these works, the proportional controllers are used to obtain an SM power reference based on their SoC error, while PI regulators are used to track these references without steady-state errors.

One major problem with these techniques is that the controller gain selection becomes challenging when batteries exhibit different capacities. Furthermore, large SoC balance errors can result in SM voltage references that saturate the modulator or in high currents that break the safe power limits of some battery packs [70]. Therefore, these inter-SM control schemes may not be suitable for SL-BESS applications that present significant capacity and power rating differences among their BPs.

In [65] and [33], inter-SM SoC balancing strategies specially designed for SL-BESS based on the CHB converter with a PS-PWM stage have been recently introduced. In these techniques, power references for each SM are generated by a weighting factor policy

instead of using proportional controllers. In this way, the proposed techniques consider the SoC, capacity, and voltage of each BP to obtain the SM power references. Despite the fact that this weighing factor-based SoC control scheme can generate power references that always reduce the SoC balancing errors among SLBs, over-modulation in the PS-PWM stage due to large capacity differences among battery modules cannot always be avoided for the full range of SoC [33]. Moreover, the PI controllers used to regulate the active power of each SM also lack a mechanism to limit the SM powers without affecting the current control [70].

A different approach to achieve inter-SM energy balance is to use sorting methods [73], [79]–[81], which are usually implemented with an LS-PWM or NLC modulation stage. In the sorting SoC balancing control schemes, a priority list is created based on the SoC balancing error of each BP and the instantaneous arm current sign. Then, a voltage-matching algorithm is applied to meet the arm modulating voltage references while prioritizing the insertion of the SMs with the largest SoC imbalances. Conventional sorting SoC balancing techniques offer fast balancing speed. Nevertheless, they lack the ability to constrain the instantaneous power of each BP. Thus, these methods cannot guarantee that the SLB safe power limits are satisfied. Additionally, sorting algorithms can present scalability issues for converters with a large number of cells, as its implementation often requires a fast sampling frequency to modify the high-frequency switching pulses [82].

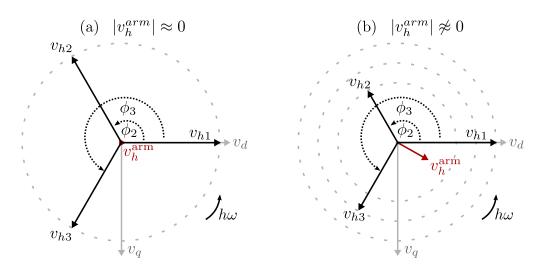

Finally, an additional challenge that affects the implementation of inter-SM SoC balancing control schemes in SL-BESS based on cascaded multilevel converters is related to the increased voltage harmonic distortion at the PWM carrier frequency and its multiples, which appears in the arm output voltage. This distortion arises when unbalanced power references among cells are imposed and/or when the batteries present different dc voltage levels, depending on the modulation strategy. As a consequence, new advanced modulation techniques, such as variable-angle PS-PWM strategies [83]–[85] are required to mitigate the low switching frequency harmonics that appear in the arm output voltage and deteriorate the output power quality of the converter.

## **1.2** Motivation and Research Vision

From the previous literature review, it is clear that the internal SoC balance in cascaded multilevel converters with batteries connected to the converter SMs adds several challenges for the converter control system. Furthermore, the standard control schemes proposed for CHB- or MMC-based BESS still present some considerable limitations by not taking into account the maximum modulation ranges, the battery module power constraints, the converter limitations to distribute the active power among SMs, and the adaptability required to consider battery aging effects over time. These issues are still more prominent for SL-BESS due to the significant differences that may be present in the BP parameters and the accelerated degradation that can be experienced for some of them [86]. Consequently, there is an opportunity to improve the CHB-based SL-BESS (CHB-SL-BESS) control schemes currently proposed in the state of the art.

During the last decades, MPC has emerged as a promising control alternative for governing energy storage systems and power converters due to its flexibility to include multiple control objectives and its ability to handle constraints [8], [51], [63]. In this control approach, the system model is used to predict the future behavior of the system state. This predicted behavior is included in an optimization problem, which is solved to obtain the best control action to achieve the control targets under consideration.

The existing battery models facilitate the real-time estimation of the SoC, battery capacity, and internal resistance [18]. As a consequence, applying proven battery models to an MPC strategy allows the control system to inherently consider the heterogeneity of SLBs in the formulation of the optimization problem. Furthermore, the operational constraints of both the converter and batteries can also be considered to compute optimal control inputs using an MPC scheme. Therefore, MPC strategies have the potential to fully exploit the multilevel converter capabilities for tracking the optimal SM power references in a CHB-SL-BESS while maintaining the safe operation of each SLB.

Motivated by the discussion above, the research vision for this thesis is focused on proposing novel MPC schemes that allow the optimal integration of SLBs directly connected to the power cells of CHB converters.